# 颖展电子高精度时钟芯片 DS3231的接口应用

### [1]. 前言

在许多单片机的测控系统和家用电器中都含有时钟显示部分,最廉价的是直接使用单片机中的定时器,辅以一定的中断服务程序,构成时钟显示部分,这种方式是几乎不需要增加新的硬件即可实现,缺点是计时误差大,同时电源掉电不能保持时钟继续运行。在相对要求较高的场合,则使用廉价的时钟芯片(如 DS1302等等)辅以备用电池,计时精度略高,可满足一般的要求。

在这篇文章中,我们重点介绍高精度时钟电路 DS3231的设计和应用。在 DS1302普及型时钟芯片,晶体均需外置,由于晶体的离散性,很难选择到精度很高的器件,同时也没有温度补偿电路,不同的温度环境下,晶体的特性也在变化,直接影响着时钟的振荡频率,较大的误差在所在所难免。而 DS3231高精度时钟芯片,将晶体和温度补偿均集成在芯片中,为提高计时精度提供了可能,实册证明,使用 DS3231时钟芯片,误差可做到一年小于一分钟,甚至部分显示器误差可小于20秒/一年。这对有相对精确时钟要求的应用场合是个理想的选择。

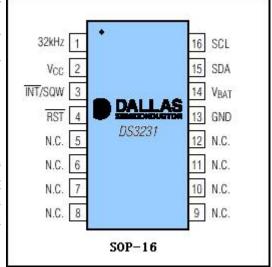

### [2]. DS3231时钟芯片结构原理

DS3231是一款高精度 I<sup>2</sup>C 实时时钟(RTC)器件,具有集成的温度补偿晶体振荡器(TCXO)。该器件包含电池输入端,断开主电源时仍可保持精确计时。集成的晶体振荡器可提高器件的长期精确度。DS3231的寄存器能保存秒、分、时、星期、日期、月、年和闹钟设置等信息。少于31天的月份,可自动调整月末日期,包括闰年补偿。时钟的工作格式为24小时或带 AM / PM 指示的12小时格式。DS3231提供两个可编程日历闹钟和一路可编程方波输出。DS3231与单片机通过 I<sup>2</sup>C 双向串行总线传输地址与数据。

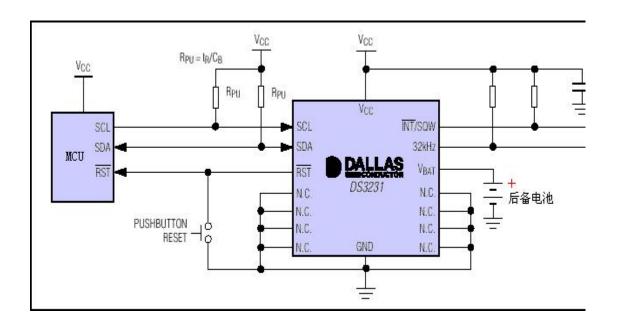

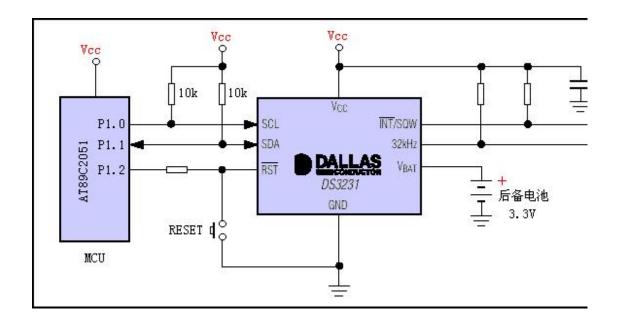

下图为 DS3231典型应用电路,图中可看出,DS3231几乎不需要外部元件。

# [3]. DS3231时钟芯片结构

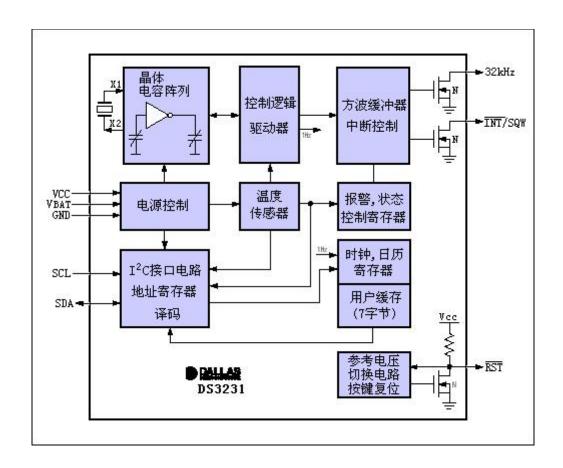

如图1所示,DS3231的主要组成部分有8个模块,划分为4个功能组: TCXO、电源控制、按钮复位和 RTC。

### 1. 32 kHz 的 TCXO

TCXO 包括温度传感器、振荡器和控制逻辑。控制器读取片上温度传感器输出,使用查表法确定所需的电容,加上 AGE 寄存器的老化修正。然后设置电容选择寄存器。仅在温度变化或者用户启动的温度转换完成时,才加载包括 AGE 寄存器变化的新值。VCC 初次上电时就会读取温度值,然后每隔64 s 读取一次。

### 2. DS3231的内部寄存器及功能

DS3231寄存器地址为00h~12h,分别用于存放秒、分、时、星期、日期及闹钟设置信息。在多字节访问期间,如果地址达到 RAM 空间的结尾12h 处,将发生卷绕,此时定位到开始位置即00h 单元。DS3231的时间和日历信息通过读取相应的寄存器来设置和初始化。用户辅助缓冲区用于防止内部寄存器更新时可能出现的错误。读取时间和日历寄存器时,用户缓冲区在任何 START 条件下或者寄存器指针返回到零时与内部寄存器同步。时间信息从这些辅助寄存器读取,此时时钟继续保持运行状态。这样在读操作期间发生主寄存器更新时可以避免重新读取寄存器。以控制寄存器(地址为0EH)为例,可以控制实时时钟、闹钟和方波输出。其各 bit 定义如下表。

控制寄存器 (OEh)

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EOSC  | BBSQW | CONV  | RS2   | RS1   | INTCN | A2IE  | A1IE  |

| 0     | 0     | 0     | 1     | 1     | 1     | 0     | 0     |

<u>BIT7位</u>:使能振荡器(EOEC)。设定为逻辑0时,启动振荡器。如果设定为逻辑1,在 DS3231电源 切换至 VBAT 时,振荡器停止。初次上电时该位清零 (逻辑0)。当 DS3231由 VCC 供电时,振荡器与 EOSC 位的状态无关,始终保持工作状态。

BIT6位:电池备份的方波使能(BBSOW)。当设定为逻辑1并且 DS3231由 VBAT 引脚供电时,在没有加载 VCC 的情况下,该位使能方波输出。当 BB-SQW 设定为逻辑0时,若 VCC 降至低于电源故障门限值,则 INT / SQW 引脚变为高阻抗。初次上电时,该位清零(逻辑0)。

BIT5位:转换温度(CONV)。该位置为1时,强制温度传感器将温度转换成数字,并执行 TCXO 算法更新振荡器的电容阵列。只在空闲期间有效。状态位 BSY=1时,禁止设定转换温度位。用户在强制控制器开始新的 TCXO 操作之前。应检查状态位 BSY。用户启动的温度转换不影响内部64 s 更新周期。用户启动的温度转换在大约2 ms 内不会影响 BSY 位。CONV 位从写入开始直到转换完成一直保持为1,转换完后,CONV 和 BSY 均变为0。在监视用户启动转换状态时,应使用 CONV 位。

#### BIT4和 BIT3位: 频

率选择(RS2和 RS1),初

次上电时,BIT4和 BIT3 设置为逻辑1。方波使能 时用于控制方波输出的 频率。RS1、RS2的逻辑 值与方波输出频率的关 系如表2所列。

# 方波輸出頻率与RSO, RS1设置关系

| RS2 | RS1 | 方波輸出頻率   |

|-----|-----|----------|

| 0   | 0   | 1Hz      |

| 0   | 1   | 1.024kHz |

| 1   | 0   | 4.096kHz |

| 1   | 1   | 8.192kHz |

BIT2位:中断控制(INTCN)。该位控制 INT / SQW 信号。INTCN 置为0时,INT / SQW 引脚输出方波; INTCN 置为1时,若计时寄存器与任一个闹钟寄存器相匹配,则会触发 INT / SQW 信号(如果也使能闹钟的话)。匹配时相应的闹钟标志总是置位,而与 INTCN 位的状态无关。初次上电时,INTCN 位置为逻辑1。

BIT1位:闹钟2中断使能(A2IE)。该位置为逻辑1时,允许状态寄存器中的闹钟2标志位(A2F)触发INT / SQW 信号(当 INTCN=1时)。当 A2IE 位置为0或者 INTCN 置为0时,A2F 位不启动中断信号。初次上电时,A2IE 位清零(逻辑0)。

BIT0位:闹钟1中断使能(A1IE)。该位置为逻辑1时,允许状态寄存器中的闹钟1标志位(A1F)触发INT / SQW 信号(当 INTCN=1时)。当 A1IE 位置为0或者 INTCN 置为0时,A1F 位不启动 INT / SQW 信号。初次上电时,A1IE 位清零(逻辑0)。

### 3. DS3231的电源控制

电源控制功能由温度补偿电压基准(VPF)和监视 VCC 电平的比较器电路提供。当 VCC 高于 VPF 时,DS3231由 VCC 供电,当 VCC 低于 VPF 但高于 VBAT 时,DS3231由 VCC 供电;当 VCC 低于 VPF 并低于 VBAT 时,DS3231由 VBAT 供电。为保护电池,VBAT 首次加到器件时振荡器并不启动,除非加载 VCC,或者向器件写入一个有效的 I2C 地址。典型的振荡器启动时间在1 s 以内。在 VCC 加电后或者有效的 I2C 地址写入后大约2 s,器件会测量一次温度,并使用计算的修正值校准振荡器。一旦振荡器运行,只要电源(VCC 或者 VBAT)有效就会一直保持工作状态。器件每隔64 s 进行一次温度测量并校准振荡器频率。

### 4. DS3231的时钟和日历 RTC

可以通过读取适当的寄存器字节获得时钟和日历信息。通过写入适当的寄存器字节设定或者初始化时钟和日历数据。时钟和日历寄存器的内容采用二-十进制编码(BCD)格式。DS3231运行于12小时或者24小时模式。小时寄存器的第6位定义为12或24小时模式选择位。该位为高时,选择12小时模式。在12小时模式下,第5位为 AM / PM 指示位,逻辑高时为 PM。

#### 5. DS3231的复位按钮

DS3231具有连接至 RST 输出引脚的按钮开关功能。若 DS3231不在复位周期,会持续监视 RST 信号的下降沿。如果检测到一个边沿转换,DS3231通过拉低 RST 完成开关去抖。内部定时器定时结束后,DS3231继续监视 RST 信号。如果信号依旧保持低电平,DS3231持续监视信号线以检测上升沿。一旦检测到按钮释放,DS3231强制 RST 为低电平并保持 tRST。RST 还可用于指示电源故障报警情况。当 VCC 低于 VPF 时,产生内部电源故障报警信号,并强制拉低 RST 引脚。当 VCC 返回至超过 VPF 电平时。RST 保持低电平大约250 ms(tREC),使供电电源达到稳定。如果在 VCC 加载时,振荡器不工作,将跳过 tREC,RST 立刻变为高电平。

#### 6. DS3231的闹钟和报警功能

DS3231包含2个定时/日期闹钟。闹钟1可通过写入寄存器07h~0Ah 设定。闹钟2可通过写入寄存器0Bh~0Dh 设定。可对闹钟进行编程(通过控制寄存器的闹钟使能位和 INTCN 位),从而在闹钟匹配条件下触发 INT / SQW 输出。每个定时/日期闹钟寄存器的第7位是屏蔽位。当每个闹钟的屏蔽位均为逻辑0时,只有当计时寄存器中的值与存储于定时/日期闹钟寄存器中的对应值相匹配时才会告警。闹钟也可以编程为每秒、分、时、星期或日期重复告警。当 RTC 寄存器值与闹钟寄存器的设定值相匹配时,相应的闹钟标志位 A1F 或 A2F 置为逻辑1。如果对应的闹钟中断使能位 A1IE 或 A2IE 也置为逻辑1,并且 INTCN 位置为逻辑1,闹钟条件将会触发 INT / SQW 信号。RTC 在时间和日期寄存器每秒更新时都会检测匹配情况。

### 7. DS3231的 I<sup>2</sup>C 总线时序,数据交换及其格式及编程注意事项

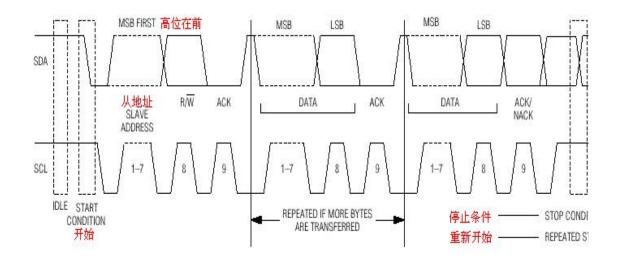

DS3231在 I2C 总线上作为从器件。通过执行 START 命令并且在验证器件地址后才可以访问。然后寄存器可以被访问直到执行一个 STOP 命令为止。

所有在 I2C 总线上传输的地址包长度均为9位,它包括7个地址位,1个 R / W 控制位和1个应答位 ACK,如果 R / W 为1,则执行读操作;如果 R / W 为0,则执行写操作。从机寻址后,必须在第9个 SCL(ACK)周期通过拉低 SDA 做出应答,若从机忙或者无法响应主机,则应在 ACK 周期内保持 SDA 为高。然后主机发出 STOP 状态或者 REP START 状态重新开始发送。地址包包括从机地址和称为 SLA+R 或者 SLA+W 的 READ 或者 WRITE 位。地址字节的 MSB 首先被发送。所有1111xxxx 的地址均保留。以便将来使用。

所有在 I2C 总线上传送的数据包长度均为9位,它包括8个数据位和1个应答位。在数据传送中,主机产生时钟及 START 与 STOP 状态,而接收器响应接收。应答是由 ACK 在第9个 SCL 周期拉低 SDA 实现的。如果接收器拉高 SDA,则发送 NACK 信号。如果接收器由于某种原因不能接收更多数据,应在最后一个数据字节后发出 NACK 信号告诉发送器停止发送,首先发送数据的 MSB。

下图为 DS3231与 MCUI<sup>2</sup>C 总线数据交换时序:

DS3231通过双向数据线 SDA 和时钟线 SCL 与外界进行数据交换,从其时序关系可看出, DS3231 有两种操作方式:

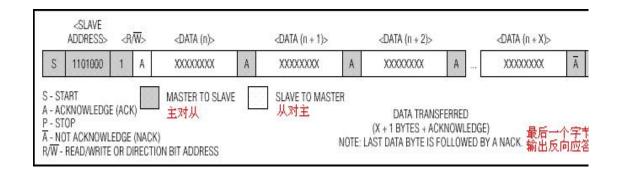

写操作:把 SDA 数据线上的数据按 RAM 指定的首地址(Word Address)依次写入 N 个字节数据。主器件首先传输从器件的地址字节,紧跟着是一系列数据字节。从器件每收到一个字节后返回一个应答位 ACK。其格式下图所示。

|        | <\$LAVE<br>ADDRESS> | ∢R | /W> | <word (f<="" address="" th=""><th>1)&gt;</th><th><data (n)=""></data></th><th>40000000</th><th><data (n="" +="" 1)=""></data></th><th></th><th></th><th><data (n="" +="" th="" x)<=""><th></th></data></th></word> | 1)>  | <data (n)=""></data> | 40000000 | <data (n="" +="" 1)=""></data>    |   |    | <data (n="" +="" th="" x)<=""><th></th></data> |     |

|--------|---------------------|----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|----------|-----------------------------------|---|----|------------------------------------------------|-----|

| S      | 1101000             | 0  | Α   | XXXXXXXX                                                                                                                                                                                                           | A    | XXXXXXXXX            | A        | XXXXXXXXXX                        | A | ][ | XXXXXXXXXX                                     | Α   |

| P - ST | CKNOWLEDG<br>TOP    |    |     | SLAVE TO MAS<br>从对主<br>ION BIT ADDRESS                                                                                                                                                                             | STER | MASTER T<br>主对从      |          | DATA TRANSF<br>(X + 1 BYTES + ACK |   |    | 数据发送<br>X=1个字节+─~                              | 个应答 |

读操作:按 RAM 指定的首地址依次读取 N 个字节数据,主器件首先传送从器件地址。从器件返回一个应答位。随后是从器件传输的一系列数据字节。主器件收到除最后一个字节外的所有字节后返回一个应答位。在收到最后一个字节后,返回一个"非应答位"NACK。其格式下图所示。

上述读写操作信号中: S 为起始信号(START), 1101 000为 DS3231的口地址, A 为应答信号 ACK, A 为非应答信号 NACK, P 为停止信号(STOP)。主器件产生所有的串行时钟和 START、STOP 条件, 通过传输 STOP 和重发 START 条件使其停止。

### 4. DS3231与 AT89C2051单片机的接口电路

其实,可以使用 AT89C2051单片机的任何两个 I/O 口与 DS3231相连接,复位部分也可取消。编程时需认真分析 DS3231的时序,哪怕一个应答位的编程时序错误,也不能正确读写 DS3231。同时需注意,因为 C51单片机的特点,在将 SDA 拉低后(此时为输出口),如果下一步是当做输入口,结束任务后应将此端口拉高,否则 DS3231的输出不能使该输出口置1。

更详细的数据手册,请阅读 [DS3231数据手册] English

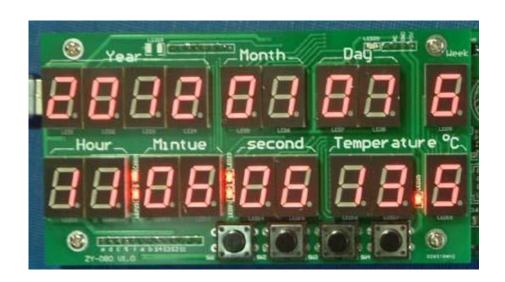

下图为一款 DS3231实验板实物图